Add to Cart

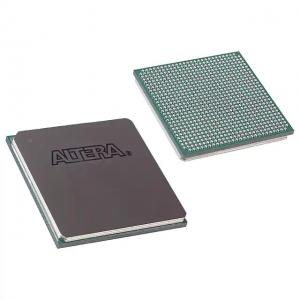

Componentes electrónicos industriales FBGA-780 de EP4SGX110DF29C4N

| Cualidad de producto | Valor del atributo |

|---|---|

| Intel | |

| FPGA - Arsenal de puerta programable del campo | |

| Stratix IV GX | |

| Entrada-salida 372 | |

| 900 milivoltio | |

| 0 C | |

| + 70 C | |

| SMD/SMT | |

| FBGA-780 | |

| Bandeja | |

| Tarifa de datos: | 600 Mb/s a 8,5 Gb/s |

| Serie: | Stratix IV GX |

| Marca: | Intel/Altera |

| Frecuencia de funcionamiento máxima: | 600 megaciclos |

| Humedad sensible: | Sí |

| Número de transmisores-receptores: | Transmisor-receptor 8 |

| Tipo de producto: | FPGA - Arsenal de puerta programable del campo |

| Cantidad del paquete de la fábrica: | 36 |

| Subcategoría: | Lógica programable ICs |

| Marca registrada: | Stratix |

Resumen de la característica

La lista siguiente resume las características de la familia del dispositivo de Stratix IV:

■Hasta 48 transmisores-receptores CDR-basados lleno-a dos caras en Stratix IV GX y dispositivos de GT que apoyan tarifas de datos hasta

8,5 Gbps y 11,3 Gbps, respectivamente

■Pre-énfasis programable del transmisor y conjunto de circuitos de la igualación del receptor para compensar pérdidas dependientes de la frecuencia

en el medio físico

■Consumo de energía medio físico típico del accesorio (PMA) de 100 mW en 3,125 Gbps y 135 mW en 6,375 Gbps por

canal

■72.600 a 813.050 LEs equivalente por el dispositivo

■Kb 7.370 a 33.294 de la memoria aumentada de TriMatrix que consiste en tres tamaños de bloque de RAM para ejecutar memoria verdadera del dual-puerto

y almacenadores intermediarios del primero en entrar, primero en salir

■Bloques de alta velocidad del procesamiento de señales digitales (DSP) configurables como 9 x 9 pedazo, 12 x 12 pedazo, pedazo 18 x 18, y 36 x lleno-precisión mordida 36

multiplicadores en hasta 600 megaciclos

■Hasta 16 relojes globales (GCLK), 88 relojes regionales (RCLK), y 132 relojes de la periferia (PCLK) por el dispositivo

■Ayuda para los interfaces externos de alta velocidad de la memoria incluyendo RDA, DDR2, DDR3 SDRAM, RLDRAM II, QDR II, y QDR II+

SRAM en hasta 24 bancos modulares de la entrada-salida

■Ayuda de alta velocidad de la entrada-salida de LVDS con el serializador/el deserializer (SERDES), la alineación dinámica de la fase (DPA), y el conjunto de circuitos de los suave-CDR en

tarifas de datos hasta 1,6 Gbps

■Ayuda para los estándares fuente-síncronos del autobús, incluyendo SGMII, GbE, SPI-4 fase 2 (nivel de POS-PHY 4), SFI-4.1, XSBI,

UTOPÍA IV, NPSI, y CSIX-L1

■Pinouts para los dispositivos de Stratix IV E diseñados para permitir la migración de diseños de Stratix III a Stratix IV E con impacto mínimo del PWB.